### John Swindle, Precept Technologies Roland Scherzinger, Agilent Technologies

# CompactPCI: Functional Design Verification of Communication Equipment

**Agilent Technologies** Innovating the HP Way

### Agenda

- Motivation to convert to CompactPCI

- Generic features of CompactPCI

- Where CompactPCI fits in the system: PCI architecture

- Verifying cellular base station transmitter/receiver modules

- Conclusion

## Motivation to Convert to CompactPCI

- Reduced design time

- Reduced manufacturing cost

- Reduced support cost

- You can and must use PCI!

- You aren't alone!

Analytical tools based on concepts developed by Intel

**Agilent Technologies**

- Platform independence; industry-standard bus

- Up to eight cards per bus

- Expandable to 256 buses per system

- Mechanical, electrical and logical specification

- Hot swap capability

- Low power consumption

- Efficient burst transactions

- Bus speed to 66MHz and bus width to 64-bit

- Concurrency

- Peer-to-peer bus mastering

- Hidden arbitration

- Low pin count

- Parity

- Three address spaces

- Software configurable

- Industry standard software

- Software transparency for ISA support and legacy IDE support

- User-defined pins

- System Management Bus

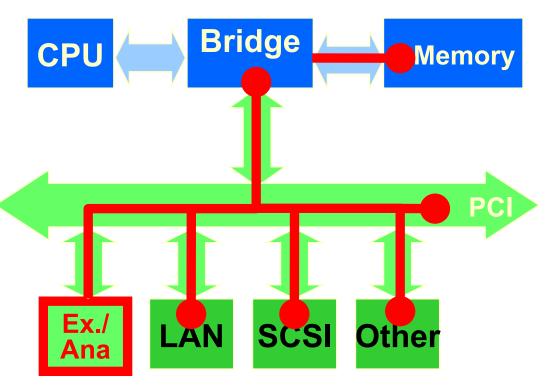

### Where Is PCI?

Page 8

### **PCI Form Factors**

**CompactPCI**

Connector

Standard short PCI card Used as the expansion bus in PCs Example: LAN card **PCI** Connector CompactPCI form factor Used in telecom and embedded applications Example: transmitter/receiver cards **Agilent Technologies** Page 9

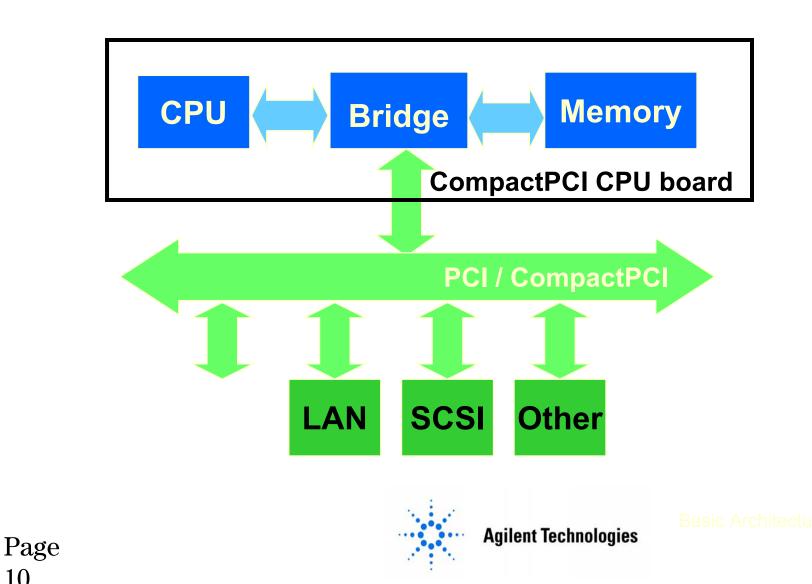

### **PCI Architecture**

10

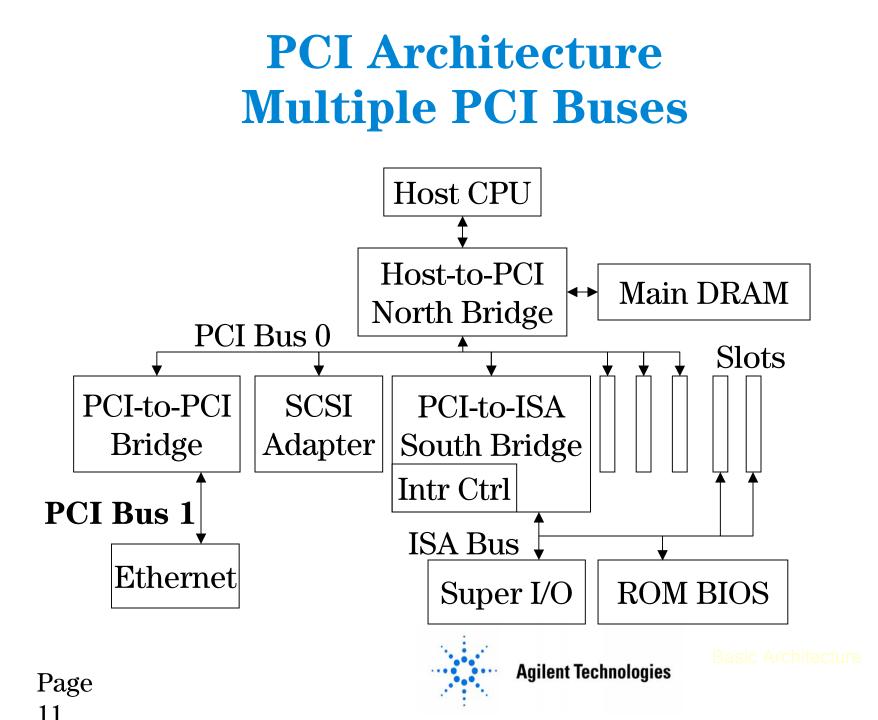

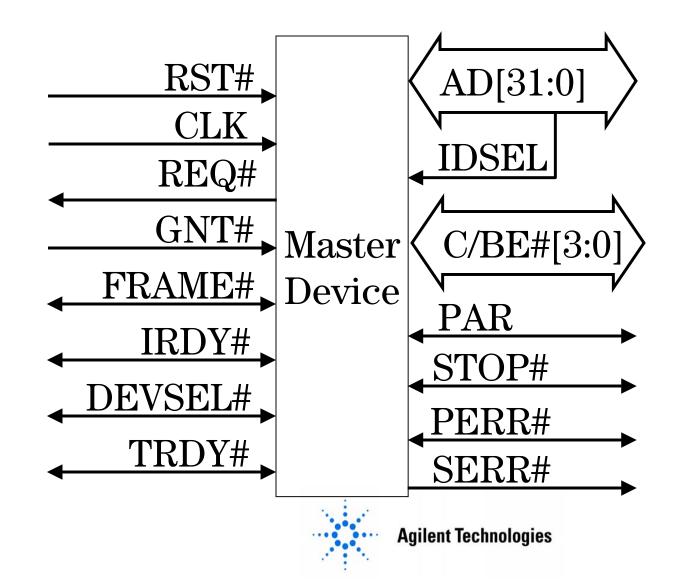

### PCI Architecture 49 Required Pins for Master

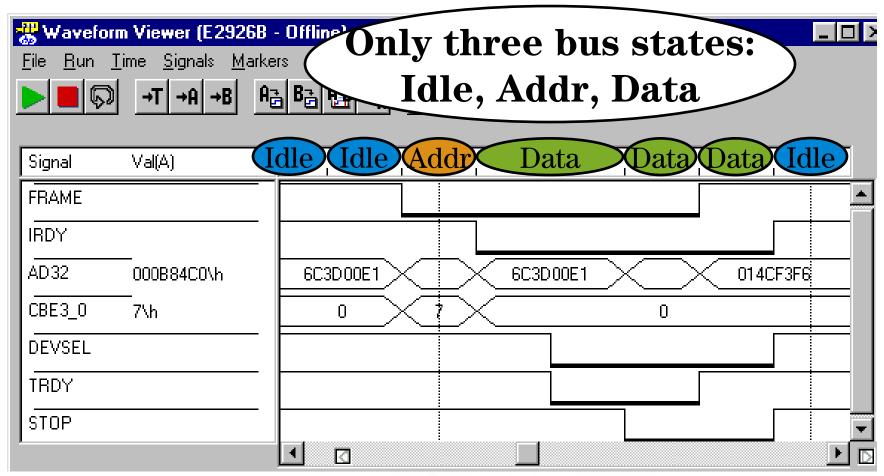

### PCI Architecture Basic Timing

### **The Typical Problems**

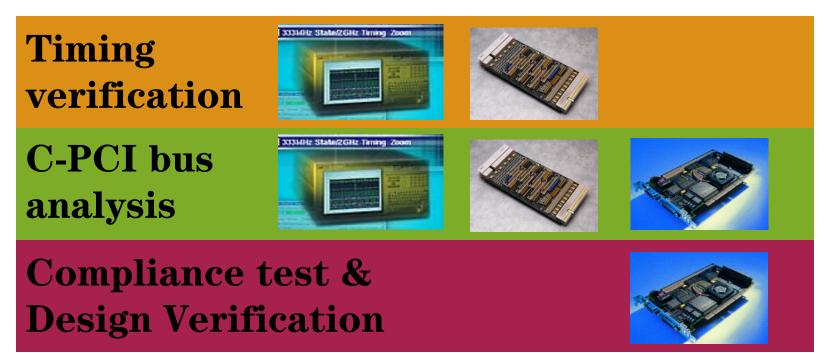

**CompactPCI Solution Portfolio Agilent Technologies and FuturePlus**

### 16700 FS3020 E2940A

**Agilent Technologies**

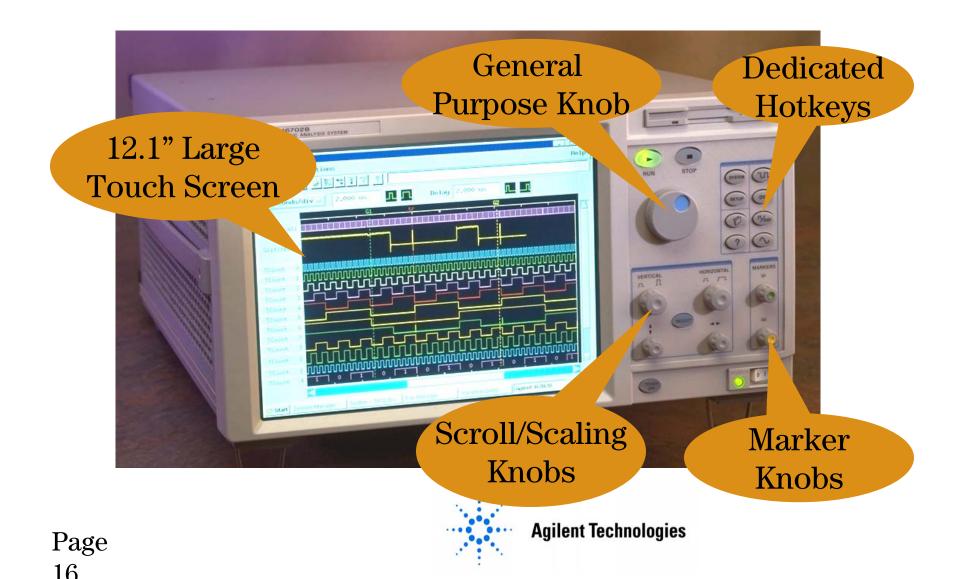

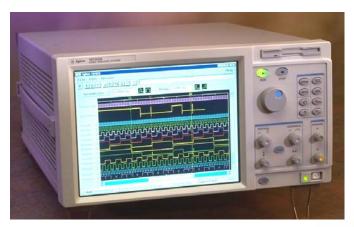

### **Agilent 16702B Frames**

## Logic Analysis Modules for 16702B Frames

- •Timing analysis to 800/400 MHz

- •State analysis to 200 MHz

- •400 MHz "Turbo" State Triggering

- •2 GHz Timing Zoom thru same probe, 16K

- •Memory depths to 32M samples

- •Up to 340 channels/group

**Agilent Technologies**

## **FuturePlus Systems**

- Agilent Channel Partner, Premier Level

- Focus on solutions for computer buses

- Provides mechanical and electrical connection from the user's bus to Agilent logic analyzers

- Provides software that configures the logic analyzer and reconstructs bus transactions from acquired data

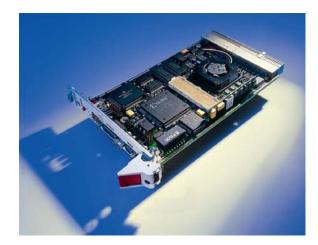

## **FuturePlus CompactPCI Bus Probe FS3020**

- For 32- or 64-bit CompactPCI Bus up to 33 MHz

- Inverse assembler, state and timing analysis

- Monitors system arbiter

- Requires 4 to 7 logic analyzer pods

- Includes extender function and test points

Also available as Agilent product FSI-60021

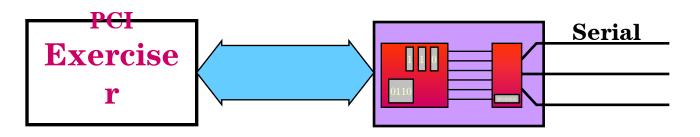

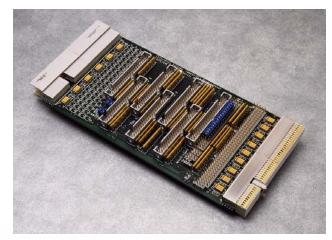

## Agilent E2940A Exerciser/Analyzer Key Features

- Single 3U CompactPCI card

- 66 MHz PCI Analyzer / 33 MHz PCI Exerciser, master/target

- Full 32/64-bit PCI data, address and command support

- Supports all PCI signals

- Hot swappable

**Agilent Technologies**

## Agilent E2940A Exerciser/Analyzer Key Features

- PCI protocol check and setup and hold timing analysis (250 ps resolution)

- Real-time and statistical analysis of PCI bus performance

- Up to 4M PCI state memory

- Up to 512 KB on-board data memory

- 24 pattern terms and 64-level trigger sequencer

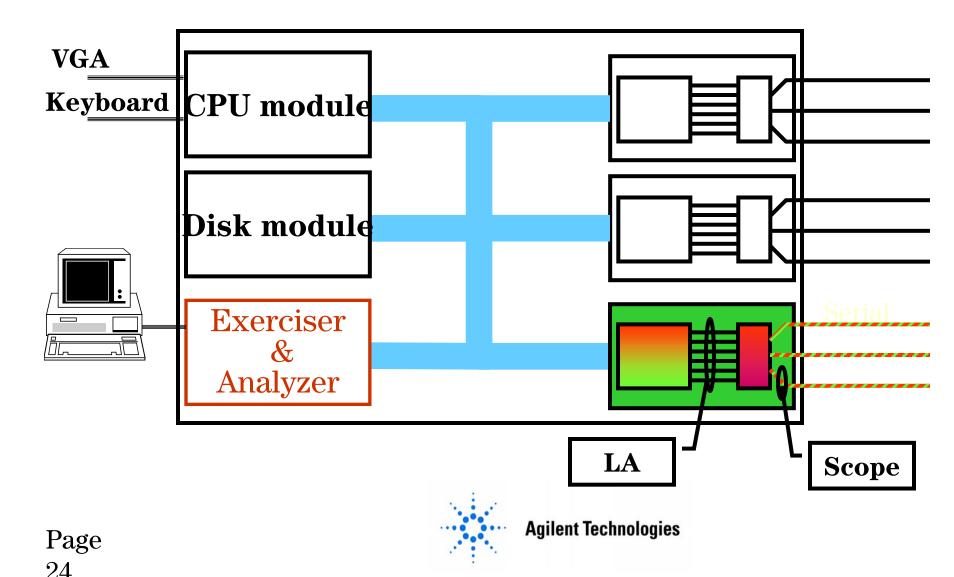

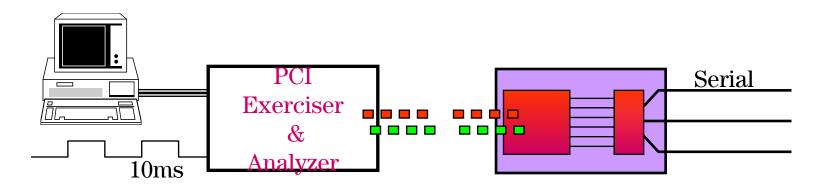

## Agilent E2940A Exerciser/Analyzer HW & SW Control

- Control via systemunder-test (SUT) host, or

- External control by serial or fast parallel interface for transparency to SUT

- Control via GUI and/or C-API

- Protocol Permutation

- System Verification Pkg Page 22

| 🚜 Master Transactions (E2926B - Offline)                               |

|------------------------------------------------------------------------|

| <u>F</u> ile <u>E</u> dit <u>S</u> earch <u>H</u> elp                  |

| // Master Transactions                                                 |

| 1// {                                                                  |

| // m_xact(busaddr = b8000\h, cmd = mem_wri                             |

| <pre>// m_data(data = 8f458f42\h); // m_last(data = 8f548f53\h);</pre> |

| <pre>// m_last(data = 8f548f53\h);</pre>                               |

| [// · }                                                                |

## What Does the Agilent E2940A CompactPCI Exerciser / Analyzer Do?

- At a central position, it provides an excellent

- Measure

- performance

- •Generate traffic

- Check PCI protocol

Page

23

• Check PCI timing

### **Example: Verify Transmitter/Receiver Modules of a Cellular Base Station**

### **Initial Module Bring-Up**

### System Monitor:

In the early phase of module bring-up, the master capability of a CompactPCI Exerciser is heavily used to monitor and control the systems/module status.

### **Initial Module Bring-Up**

E2940A checks 53 protocol rules in real time, not sampled and post-processed.

Basic setup and hold timing can also be verified. For more accuracy, use 16700 logic analyzer.

**Agilent Technologies**

Protocol Check (E2926B on COM1)

Image: Comparison of Communication

File

Rule

Help

Status

Rules violated:

1

Rules violated:

1

Read from card

First violated Rule:

LAT 0

Clear

| Rule (double-click for description)                                                                                                        | Mask                            | Status               |  |

|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------------------|--|

| SEM 8                                                                                                                                      | Disabled                        | 0K                   |  |

| SEM 9                                                                                                                                      | Disabled                        | 0K                   |  |

| SEM 12                                                                                                                                     | Enabled                         | OK                   |  |

| SEM 13                                                                                                                                     | Enabled                         | 0K                   |  |

| LAT 0                                                                                                                                      | Enabled                         | ERROR                |  |

| HP E2920 Message                                                                                                                           |                                 | <mark>ж</mark>       |  |

| <b>i</b> LAT 0:Targets are requir<br>the initial data phase of<br>within 16 clocks, subser<br>within 8 clocks. (PCI Sp<br>Rules 25 and 26) | a transaction<br>quent data pha | ases <mark>IK</mark> |  |

### **Functional Transmitter Module Test**

- Correct handling of data blocks sent to and from the transmitter/receiver module

- Susceptibility to data delays

- Handling of data queues

### **Functional Transmitter Module Test**

| din<br>dir             | laster                    | Tran                     | sact                            | tions                             | : (E2926B - Offline)                                                                                                                  |

|------------------------|---------------------------|--------------------------|---------------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| <u>F</u> ile           | <u>E</u> dit              | <u>S</u> ear             | ch <u>l</u>                     | <u>H</u> elp                      |                                                                                                                                       |

| <br>  <br>  <br>  <br> | {<br>m_<br>m_<br>m_<br>m_ | xac<br>dat<br>dat<br>dat | t (b<br>a (d:<br>a (d:<br>a (d: | usac<br>ata<br>a <mark>M</mark> a | ctions<br>ddr = b8000\h, cmd = mem_write);<br>= 8f358f32\h);<br>aster Conditional Start (E2926B - Offline)<br>Help                    |

|                        | m                         | _dat<br>_las             | =                               | a —                               | Master Start<br>Immediate<br>Pattern AD32=b8xxx\h && addr_phase=1 Edit<br>Wait after pattern seen<br>No<br>Clockdelav 10 Clock Cycles |

### **Premature Terminations**

| 🖑 Transaction                        | n Lister (E2927A on COM1)          |   |

|--------------------------------------|------------------------------------|---|

| <u>F</u> ile <u>R</u> un <u>S</u> ea | arch <u>H</u> elp                  |   |

| ▶ <b>■</b> ଭ                         | 📲 🖓 付 Goto:                        |   |

| 14:                                  | Memory Write A = fecfdfc4 -RETRY 2 | 1 |

| 43:                                  | Memory Write A = fecfdfc4 -RETRY 2 |   |

| 72:                                  | Memory Write A = fecfdfc4 -RETRY 2 |   |

| 101:                                 | Memory Write A = fecfdfc4 -RETRY 2 |   |

| 130:                                 | Memory Write A = fecfdfc4 -RETRY 2 |   |

| 159:                                 | Memory Write A = fecfdfc4 -RETRY 2 |   |

| 188:                                 | Memory Write A = fecfdfc4 -RETRY 2 |   |

| 217:                                 | Memory Write A = fecfdfc4 -RETRY 2 |   |

**Agilent Technologies**

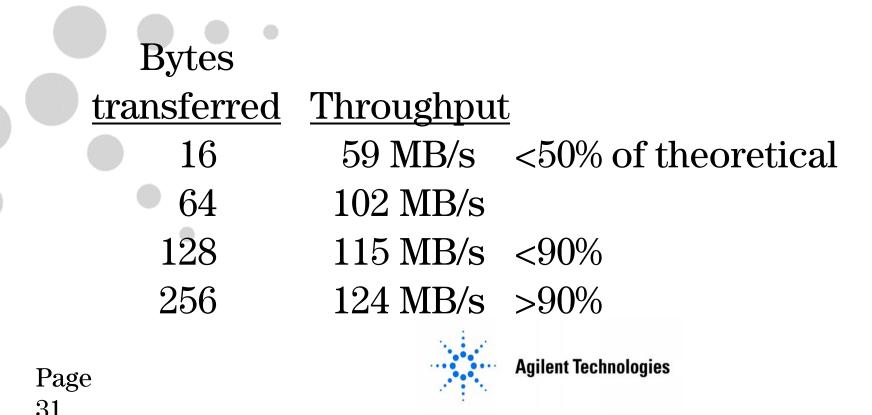

### **Performance is #1 Concern**

Most other problems are solved by the availability of high-quality components, boards and systems from many vendors. The maturity of the specification usually assures hardware interoperability of basic designs.

Page

30

A little latency consumes a lot of bandwidth. Example: 32-bit, 33MHz bus with only three wait states in the entire transaction.

Surprised? What causes performance problems?

- Multiplexing (without split transactions) means no pipelining. Much of the latency is explicitly visible on the bus. PCI is tuned for thruput at the expense of latency.

- Latency rules don't solve the throughput issues.

- Depth of topology, delayed transactions and transaction reordering affect latency.

**Agilent Technologies**

Recommendations for performance:

- Choose agents that have low latency

- Choose agents with deep buffers

- Choose agents which use optimized commands

- Choose bridges with deep buffers and capable of handling multiple delayed transactions

- Measure performance with the Agilent analyzer

**Agilent Technologies**

The Analyzer has better visibility and control than other agents on the bus, better than that of the host bridge.

Much of the PCI latency and throughput are transparent to software, that is, not under the control of software or the host processor. Only coarse performance measurements may be performed by the host processor's software.

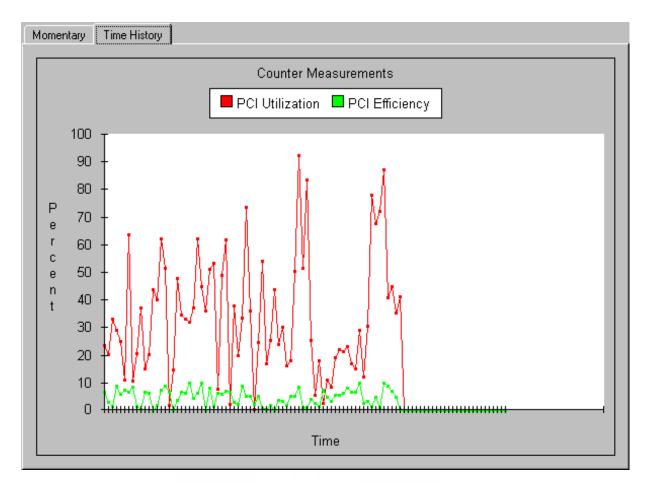

Analyzer needs to be able to:

- Measure bus utilization

- Measure bus efficiency

- Track delayed transactions

- Track sequences of events (transaction order)

- Exercise the system across many bridges (using multiple Exercisers and Analyzers)

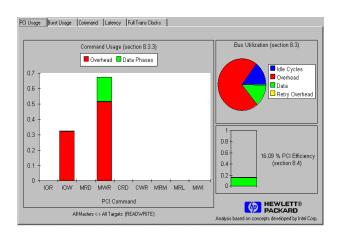

### **Performance Measurements: Real Time Counter**

High utilization and low efficiency indicate a potential problem

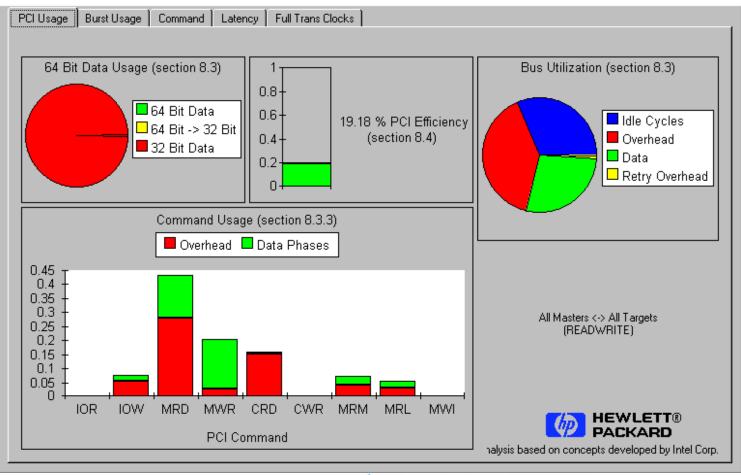

### **Performance Measurements: Utilization and Efficiency of Commands**

**Agilent Technologies**

### Performance Report (partial)

#### 1.2 Statistical Base

\_\_\_\_\_

| Test covered                  | 131512 clocks  |

|-------------------------------|----------------|

| Test covered                  | 0.00398521 sec |

| No of captured address cycles | 6129 clocks    |

| No of captured data cycles    | 37060 clocks   |

| Number of Bytes transferred   | 138548 bytes   |

| No of Interrupts occurred     | 0              |

#### 2 BASIC BUS STATISTICS

| <br> | <br>_ | _ | _ | _ | _ | _ | _ | _ | _ | _ | _ | _ | _ | _ | _ | _ | _ |

|------|-------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| <br> | <br>_ | _ | _ | _ | _ | _ | _ | _ | _ | _ | _ | _ | _ | _ | _ | _ | _ |

|      |       |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|      |       |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| PCI Throughput            | 34.7655  | Megabytes/sec |

|---------------------------|----------|---------------|

|                           | 278.1242 | Megabits/sec  |

| PCI Utilization           | 68.67 %  |               |

| Non-retry PCI Utilization | 67.80 %  |               |

| PCI Efficiency            | 19.18 %  |               |

| Non-retry PCI Efficiency  | 19.42 %  |               |

### System Validation Package: Busload Generator

SVP Scenario 1 Scenario 1 System Memory Read System Memory Read Peer-To-Peer Traffic Master-To-Target Traffic Susload Generator Testcard 1 CPU to Testcard address space Testcard to system memory CPU+Testcard to system memory Protocol Checker PCI Configuration scan

loaded system without having to populate with more cards. Page 39

|                          |                 |                                                                                      |                           | TEST SI               | ETUP                  |              |     |  |

|--------------------------|-----------------|--------------------------------------------------------------------------------------|---------------------------|-----------------------|-----------------------|--------------|-----|--|

| <u>N</u> ame             | Busload Ge      | nerator                                                                              |                           |                       |                       |              |     |  |

| <u>D</u> escription      |                 |                                                                                      |                           |                       |                       |              |     |  |

| <u>F</u> unction         | busload         | •                                                                                    |                           |                       |                       |              |     |  |

|                          | NOTE: disa<br>D | merating self-traffi<br>ble PPR for testca<br>ata Path: Testcar<br>ested Devices: Ar | ard for cor<br>d master - | rect band<br>> Testca | width re<br>ird targe | esults<br>et |     |  |

|                          |                 |                                                                                      |                           |                       |                       |              |     |  |

| <u>A</u> ddress (Spac    | e/Offset)       | мем 🔽                                                                                | 000B8                     | 000\h                 |                       |              |     |  |

| <u>S</u> tart Delay (do  | l:hh:mm:ss      | 0:00:00:00                                                                           |                           |                       |                       |              |     |  |

| D <u>u</u> ration (dd:hl | h:mm:ss)        | 0:00:01:00                                                                           |                           |                       |                       |              |     |  |

| <u>B</u> ytes to Trans   | fer             | 4096                                                                                 |                           |                       |                       |              |     |  |

| Band <u>w</u> idth %     |                 | 61                                                                                   |                           |                       | <u> </u>              | }            | · · |  |

## **System Validation Package: Protocol Permutation and C-API**

- Protocol Permutation and Randomization (PPR) allows more scenarios and corner cases to be checked in much less time with less programming and manual effort.

- Test parameters are permuted and randomized by PPR within limits set by the engineer.

- "Characterizing the performance of a PCI system typically took 2-3-4 days, almost a week. Now we can do it in as little as 15 minutes." Gregory McKnight, IBM Page 40 Performance Lab.

### Conclusions

- CompactPCI systems require verification at the protocol, data and messaging levels.

- Active test equipment sitting on the PCI bus gives an excellent insight into the system under test.

- Use test equipment suited for the measurement.

- Agilent PCI Exerciser/Analyzers extend the classical debugging environment by adding predictable traffic generation capabilities.

- Agilent and FuturePlus test equipment supports the conversion from proprietary buses to PageompactPCI.

Agilent Technologies

### **Thank You!**

**Agilent Technologies**